【導讀】在功率變換器應用中,寬帶隙(WBG)技術日益成為傳統(tǒng)硅晶體管的替代產品。在某些細分市場的應用場景中,提升效率極限一或兩個百分點依然關系重大,變換器功率密度的提高可以提供更多應用優(yōu)勢,在這種情況下采用基于氮化鎵(GaN)晶體管的解決方案意義重大。

引言

在功率變換器應用中,寬帶隙(WBG)技術日益成為傳統(tǒng)硅晶體管的替代產品。在某些細分市場的應用場景中,提升效率極限一或兩個百分點依然關系重大,變換器功率密度的提高可以提供更多應用優(yōu)勢,在這種情況下采用基于氮化鎵(GaN)晶體管的解決方案意義重大。與傳統(tǒng)硅器件相類似,GaN晶體管單位裸片面積同樣受實際生產工藝限制,單個器件的電流處理能力存在上限。為了增大輸出功率,并聯(lián)配置晶體管已成為設計工程師可以考慮的選項之一。應用晶體管并聯(lián)技術在最大限度提升變換器輸出功率的同時,也帶來了電路設計層面的挑戰(zhàn)。

并聯(lián)晶體管的設計挑戰(zhàn)

在應用晶體管并聯(lián)技術時,首先需要考慮的是并聯(lián)晶體管的通態(tài)電阻(RDS(on))。理想情況下,所選器件應均勻匹配,以確保靜態(tài)電流在并聯(lián)晶體管之間平均分配。其次,在動態(tài)開關過程中,如果晶體管柵極缺乏對稱性,不僅會導致流經(jīng)晶體管的電流分配不平衡,動態(tài)電流和電路寄生參數(shù)將會導致高頻振蕩電壓。如果這些無法解決這些問題,將可能導致晶體管損壞。

盡管傳統(tǒng)硅晶體管的并聯(lián)配置技術已經(jīng)十分成熟,但對于GaN器件并聯(lián)技術研究還鮮有涉及。考慮到GaN器件驅動的特殊性以及其高速開關特性,我們將首先從GaN器件驅動電路設計開始介紹。

正確設計驅動電路

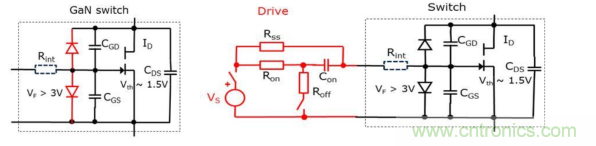

諸如英飛凌科技 CoolGaN™600 V HEMT之類的GaN晶體管采用了柵極p型摻雜工藝,這會將器件的柵極閾值電壓轉換為很低的正向電壓(1.0V~1.5V)。該結構中柵極形成的pn結正向電壓(VF)約為3.0 V,電阻為幾歐姆,與柵極電容CG并聯(lián)。因此,CoolGaN™晶體管驅動電路與傳統(tǒng)硅晶體管存在很大差異。柵極驅動過程中,一旦達到Miller平臺,柵極電壓就被鉗位到接近VF的值,這意味著在硬開關應用中需要負電壓來關斷晶體管。同時,CoolGaN™ 器件在穩(wěn)態(tài)導通狀態(tài)和開關瞬態(tài)所需驅動也有所不同。

針對CoolGaN™晶體管特性設計的柵極驅動電路如圖1所示。為確保柵極驅動正常,驅動電壓VS的峰值需要超過VF的兩倍(通常使用8V~10V),通過Ron提供了一條瞬態(tài)低阻抗高速AC路徑來為Con和CGS充電,然后通過RSS形成一條并聯(lián)的穩(wěn)態(tài)DC路徑。因此,柵極導通瞬態(tài)電流由Ron決定,而RSS決定穩(wěn)態(tài)二極管電流。

在柵極關斷時,CGS和Con中的電荷將快速達到平衡。此處必須確保Con大于CGS,以確保穩(wěn)態(tài)的電荷差使柵極電壓VG變?yōu)樨撝?,從而在硬開關應用中關斷晶體管。

圖1:E模式GaN HEMT等效電路(左)和建議的驅動方案(右)。

當并聯(lián)配置CoolGaN™晶體管時,可使用相同參數(shù)的RC驅動網(wǎng)絡分別連接每個并聯(lián)晶體管,再同時與傳統(tǒng)硅晶體管的標準驅動器連接。并聯(lián)的幾個晶體管只需要一個隔離型驅動器,例如隔離型EiceDRIVER™1EDI20N12AF,使用源極(OUT +)和漏極(OUT-)輸出分別實現(xiàn)晶體管的導通和關斷。當使用12V隔離電源作為柵極驅動器供電時,EiceDRIVER™內部會將其分為正向驅動電壓和-2.5V反向關斷電壓這樣可確保驅動電壓不超過晶體管柵極閾值,并大限度減小反向導通損耗。即使在低占空比情況下,EiceDRIVER™也可以保持良好的柵極電壓調節(jié)特性,從而阻止RC驅動網(wǎng)絡失壓。

電流旁路對GaN晶體管并聯(lián)配置的影響

即使每個晶體管都配置獨立的RC驅動網(wǎng)絡,并聯(lián)晶體管的源極電流仍然存在部分共享路徑,這將會對柵極驅動產生影響(見圖2)。理想情況下,所有源極電流都將從漏極流至晶體管源極,但不可避免的一種情況是,部分源極電流會從開爾文源極(Kelvin source)流出。如果這些路徑的阻抗和PCB布線不同,則并聯(lián)的CoolGaN™晶體管柵極回路中的VGS電壓可能會有所不同,小至幾毫伏的柵極電壓差異會導致幾安培的不平衡源極電流分流,導致并聯(lián)晶體管之間在開關瞬態(tài)產生劇烈振蕩。

圖2:在CoolGaN™并聯(lián)操作中,開爾文源極路徑中的高阻抗可防止發(fā)生嚴重的振蕩。

共享驅動電流路徑問題可以通過在開爾文源極路徑中引入高阻抗共模(CM)電感解決。將共模電感器和一個1?電阻器配置在柵極和相應的Kelvin源極驅動器返回路徑之間,柵極驅動器環(huán)路中將呈現(xiàn)很小的漏感,而并聯(lián)晶體管的柵極共享路徑中將由于兩個共模電感的存在呈現(xiàn)高阻抗。選擇共模電感需要避免對柵極驅動器的驅動能力產生影響,圖3所示的SIMetrix仿真結果清楚顯示了共模電感對共享驅動電流路徑問題的抑制。

圖3:仿真結果顯示在沒有共模電感(上)和加入共模電感(下)情況下開關40A電流。

PCB優(yōu)化設計

在并聯(lián)配置晶體管時,另一個普遍關注的問題是PCB中寄生電感和電容(器件布局、PCB布線、多層PCB布局),以及所用器件中寄生電感和電容的影響。對于CoolGaN™晶體管,關鍵問題是由VGS閾值范圍和晶體管之間RDS(on)差異造成的影響。通過仿真,在SIMetrix中對CoolGaN™晶體管進行建模分析。仿真模型使用0.9V~1.6V閾值電壓和55mΩ~70mΩ的RDS(on)值的CoolGaN™并聯(lián),同時對寄生電感和PCB寄生電容電容進行建模。分析結果表明,并聯(lián)晶體管分流不均僅與所用晶體管之間的RDS(on)差異有關。在必要情況下,可以通過進行嚴格器件匹配來解決。如前文所述,使用CM電感可以避免破壞性的持續(xù)電壓振蕩。然而,遵循良好的元器件布局和PCB布線也是一個關鍵因素。電源環(huán)路和柵極驅動環(huán)路必須保持較小且對稱,同時還要確保開關節(jié)點的寄生電容盡可能低。

積累實踐經(jīng)驗

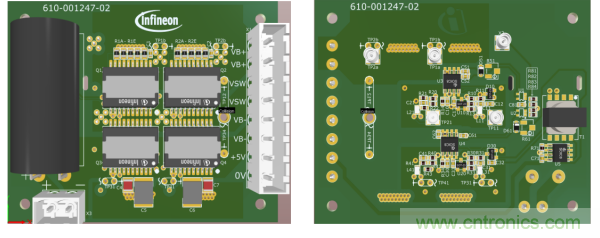

了解挑戰(zhàn)及其解決方案的最佳方法是在實驗室進行試驗。為此,英飛凌開發(fā)了并聯(lián)半橋評估板,其中應用了四個70mΩ IGOT60R070D1 CoolGaN™晶體管。該評估板遵循了以上介紹的設計準則,可以為評估和設計開發(fā)提供了一個良好的基礎。評估版還提供了大量測試點。需要注意的重要一點是,對于某些測量點,需要高帶寬隔離差分探頭,并且在使用前矯正以確保準確的波形采集。

通過連接外置電感,該評估板可用于降壓或升壓電路(buck circuit or boost circuit)測試、雙脈沖(double pulse test)測試以及脈沖寬度調制(PWM)運行。評估板還適用于數(shù)千瓦功率等級或高開關頻率至1MHz的軟開關和硬開關應用。模塊化設計簡化了測試配置流程,除了板載100µF,450V的大容量電容之外,額外的連接器允許再增加一個母線電容。 該組件與另外兩個高頻旁路電容器一起,確定了450V的輸出或母線電壓等級。在安裝合適的散熱器、導熱片和風扇的情況下,評估板可在硬開關或軟開關下以高達28A的連續(xù)電流,或峰值電流70A運行。 死區(qū)時間電路中的電位計也包括在評估板內,可通過RC網(wǎng)絡實現(xiàn)延遲接通,以及通過二極管實現(xiàn)無延遲關斷。

圖4:并聯(lián)半橋CoolGaN™評估平臺。

總結

盡管硅晶體管并聯(lián)配置已經(jīng)十分成熟,GaN晶體管并聯(lián)配置對于許多設計工程師而言仍然存在挑戰(zhàn),采用不同于傳統(tǒng)硅器件的柵極驅動電路是并聯(lián)配置的關鍵。由此開始,GaN晶體管并聯(lián)配置與硅晶體管相類似,但不完全相同。為保證并聯(lián)晶體管均流,需要在設計階段對PCB布線和器件選型進行優(yōu)化。針對旁路電流對并聯(lián)GaN晶體管的影響,在柵極和開爾文源極路徑中加入合適的共模電感是必不可少的,這將有助于最大限度減小電壓震蕩。

免責聲明:本文為轉載文章,轉載此文目的在于傳遞更多信息,版權歸原作者所有。本文所用視頻、圖片、文字如涉及作品版權問題,請電話或者郵箱聯(lián)系小編進行侵刪。