【導(dǎo)讀】在設(shè)計(jì)初期就注重干擾抑制和工作可靠性要比以后再增加其它措施更具經(jīng)濟(jì)性。在自適應(yīng)電纜均衡器的設(shè)計(jì)早期采用了這些設(shè)計(jì)建議�,就可以提高系統(tǒng)的性能��,無(wú)需今后重新設(shè)計(jì)以解決干擾與性能的問(wèn)題��。使用哪些簡(jiǎn)單技術(shù),可以將干擾降低到最低程度����,提高自適應(yīng)電纜均衡器的性能。

自適應(yīng)電纜均衡器是串行數(shù)字視頻(SDV)廣播和串行電信設(shè)備接收器前端的基本組成部分��,它們還可以用于其它類型的有線通信系統(tǒng)����。均衡器直接與傳輸線接口,恢復(fù)由電纜造成信號(hào)幅度及帶寬的損耗�。由于均衡器直接連接到電纜,因此它很容易受ESD����、EMI/RFI和器件所產(chǎn)生的噪聲影響,均衡器的工作特性也傾向于增大設(shè)計(jì)中噪聲的影響����。一個(gè)采用抗干擾自適應(yīng)電纜均衡器的魯棒系統(tǒng)也必須保持均衡器的一些良好工作特性�,如寬輸入動(dòng)態(tài)范圍����、寬信號(hào)帶寬、低殘留輸出噪聲��、高輸入回波損耗��,以及最大均衡電纜長(zhǎng)度等�����。

ESD��、EMI/RFI和器件產(chǎn)生的噪聲是有線通信系統(tǒng)中的三大主要干擾模式:ESD可以毀壞或摧毀電路內(nèi)外的有源及無(wú)源器件���;EMI/RFI會(huì)影響系統(tǒng)的信號(hào)處理�,嚴(yán)重時(shí)會(huì)造成系統(tǒng)基本功能的失效����;器件產(chǎn)生的噪聲可以影響電路的工作,降低其性能����,亦可導(dǎo)致系統(tǒng)失效。

自適應(yīng)均衡器設(shè)計(jì)的技術(shù)挑戰(zhàn)

要設(shè)計(jì)一個(gè)能應(yīng)對(duì)以上干擾的魯棒系統(tǒng)是一個(gè)不小的挑戰(zhàn)����。自適應(yīng)電纜均衡器并非簡(jiǎn)單的數(shù)字器件,這是設(shè)計(jì)者都必須仔細(xì)考慮的基本事實(shí)��。美國(guó)國(guó)家半導(dǎo)體的CLC014�、CLC012和最新的CLC034自適應(yīng)均衡器是高性能的模擬器件,它們是高增益�、高帶寬、模擬�、射頻、AGC放大器濾波器��。在正確集成情況下�,它們能與其它所有系統(tǒng)元件(包括機(jī)箱、無(wú)源元件和PCB等)共同抵御內(nèi)����、外部的干擾。一般情況下��,當(dāng)電纜長(zhǎng)度為最大時(shí)�,均衡器接收到的信號(hào)為最小�。所以���,均衡器的增益與帶寬要在最大值�����。但當(dāng)輸入端未連接�����,沒(méi)有外接信號(hào)時(shí)����,增益與帶寬也是最大��。在最大增益情況下��,即使少量的有害EMI或傳導(dǎo)干擾都會(huì)被大大地放大���,影響均衡器的正常工作����。好的PCB設(shè)計(jì)可以阻止干擾���,避免一些常見(jiàn)的均衡器應(yīng)用故障��,如:無(wú)法在給定數(shù)據(jù)速率下均衡最大電纜長(zhǎng)度����;電纜長(zhǎng)度小于最大值出現(xiàn)數(shù)據(jù)錯(cuò)誤����;當(dāng)輸入端開(kāi)路時(shí)有虛假的或隨機(jī)輸出數(shù)據(jù);信號(hào)檢測(cè)錯(cuò)誤指示�����。

這些故障是由以下原因引起的:源于系統(tǒng)機(jī)箱內(nèi)部或PCB上的EMI輻射�;邏輯器件或電源通過(guò)輸入網(wǎng)絡(luò)的元器件安裝管腳耦合到輸入端的噪聲;其它附近電路對(duì)輸入端及/或自適應(yīng)均衡器電路(AEC)的串?dāng)_�����;均衡器輸入�����、輸出電路的耦合����。ESD事件會(huì)嚴(yán)重?fù)p壞半導(dǎo)體器件����,特別是當(dāng)這些器件沒(méi)有導(dǎo)電包裝材料保護(hù)時(shí)����,更容易遭受損害,即使半導(dǎo)體器件安裝在電路上也會(huì)被損壞����。用于直接電纜接口的器件,如線路驅(qū)動(dòng)器和電纜均衡器等都按照最大ESD額定電壓而設(shè)計(jì)����。即便如此,只依賴于半導(dǎo)體器件本身來(lái)提供所有ESD防護(hù)���,而無(wú)視其額定 ESD防護(hù)值的高低�����,仍是不明智的做法����。均衡器輸入電路有通過(guò)終結(jié)電阻接地的低阻抗路徑優(yōu)點(diǎn),提高了對(duì)ESD的耐受能力��。輸入電路中使用的元器件都應(yīng)當(dāng)有足夠的ESD抵御能力�,以應(yīng)對(duì)設(shè)計(jì)中的最大ESD事件。通過(guò)適當(dāng)?shù)倪x擇與設(shè)計(jì)�����,所有的電路元器件(包括機(jī)箱�����、連接器和PCB等)均可以實(shí)現(xiàn)均衡器和其它接口器件的ESD防護(hù)�。

提高性能的設(shè)計(jì)方法

以下這些設(shè)計(jì)措施可以抵御電子干擾��,提高均衡器整體工作性能:1. 將均衡器輸入網(wǎng)絡(luò)及AEC電路與外部�����、卡上的高電平信號(hào)隔離或屏蔽開(kāi)����;2. 采用耐用的輸入電路元器件,抑制ESD事件�;3. 采用多層PCB�,用獨(dú)立的傳輸線和電源-地層�,實(shí)現(xiàn)隔離、屏蔽和ESD防護(hù)�;4. 在電源、地層間采用薄的電介質(zhì)(6mil以下)���,以提高層間電容和高頻衰減��;5. 旁路電容��、終結(jié)電阻�、集電極負(fù)載電阻以及VCC和VEE管腳焊盤與層面連接時(shí)采用兩個(gè)過(guò)孔�����;6. 不要將多根VCC和VEE管腳連接到一個(gè)過(guò)孔����,因?yàn)檫@可能引起器件中的噪聲

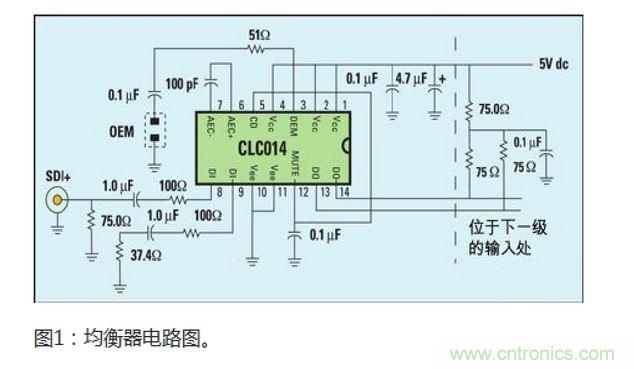

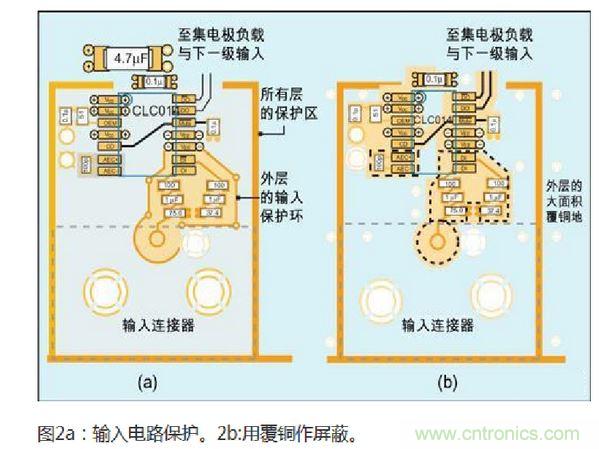

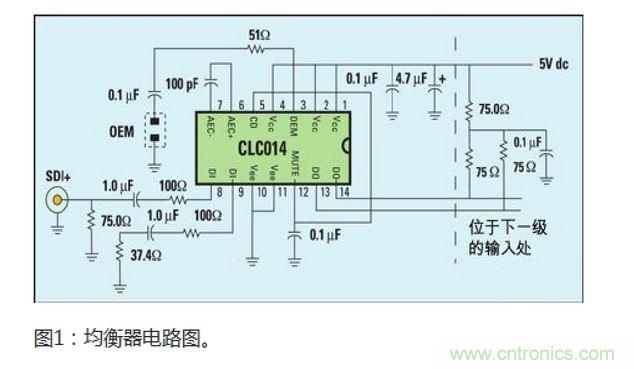

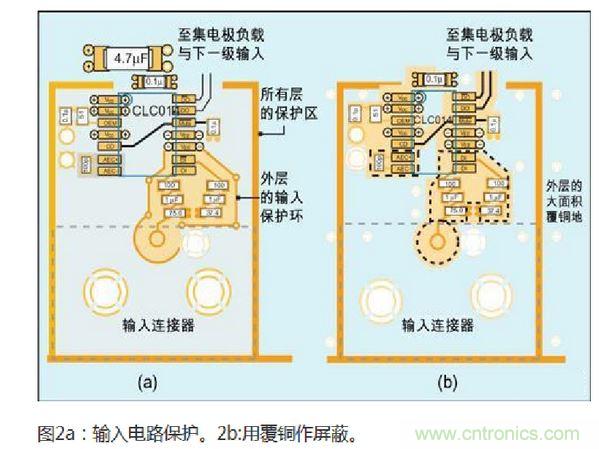

圖1所示是推薦的CLC014均衡器電路,圖2是相應(yīng)的PCB布局����。在PCB板上,采用了一些將均衡器電路與有害信號(hào)干擾隔離開(kāi)來(lái)的措施。在輸入網(wǎng)絡(luò)和AEC電容下方的電源層去除了銅箔����,消除了電源層噪聲向輸入電路和AEC電路耦合的路徑。所有層都除去了部分銅箔(深色陰影線)�����,以隔離均衡器的電路��。這些隔離帶可以防止鄰近電路通過(guò)中間層與均衡器電路的直接接觸���。這樣���,干擾信號(hào)要接近輸入電路就必須沿隔離帶走一個(gè)較長(zhǎng)的路徑�����。

這樣的做法增加了低通濾波效果��,提高了對(duì)有害信號(hào)的衰減能力��。用于提供信號(hào)環(huán)路(loop-back)功能的電纜驅(qū)動(dòng)器經(jīng)常毗鄰均衡器放置�。電纜驅(qū)動(dòng)器的輸出信號(hào)要比均衡器接收到的信號(hào)強(qiáng)很多,隔離帶有助于隔離電纜驅(qū)動(dòng)器信號(hào),降低對(duì)均衡器輸入信號(hào)的干擾��。在輸入電路周圍是一個(gè)良好接地的保護(hù)(屏蔽)環(huán)�,用于降低拾取到的RFI,如圖2a所示�����。也可以用PCB外層的覆銅代替保護(hù)環(huán)����,如圖2b。覆銅必須以約1cm的間距連接所有的地層���,以形成一個(gè)有效的屏蔽���。均衡器差分輸入放大器的共模抑制以及對(duì)稱的輸入元件布局也可以增強(qiáng)RFI抑制能力。RFI在同時(shí)被兩個(gè)輸入端接收時(shí)是一種共模信號(hào)���。具有平衡終結(jié)阻抗的對(duì)稱輸入電路布局可使RFI信號(hào)平均地到達(dá)兩個(gè)輸入端��,這樣輸入差分放大器的共模抑制功能可以消除大部分干擾信號(hào)����。