【導(dǎo)讀】半導(dǎo)體制造的工藝節(jié)點(diǎn),涉及到多方面的問(wèn)題�,如制造工藝和設(shè)備,晶體管的架構(gòu)����、材料等。半導(dǎo)體制造工藝節(jié)點(diǎn)是如何演進(jìn)的�?晶體管的架構(gòu)是怎樣發(fā)展成如今模樣的?下面��,我們就具體介紹并分析一下�����,供大家參考�。

首先���,技術(shù)節(jié)點(diǎn)是什么意思呢��?常聽(tīng)說(shuō)的�����,諸如�����,臺(tái)積電16nm工藝的Nvidia GPU�、英特爾14nm工藝的i5,這個(gè)長(zhǎng)度的含義�,具體的定義需要詳細(xì)給出晶體管的結(jié)構(gòu)圖才行,簡(jiǎn)單地說(shuō)����,在早期,可以認(rèn)為是晶體管的尺寸����。

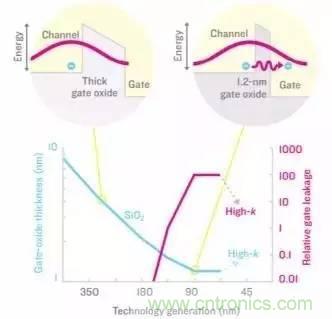

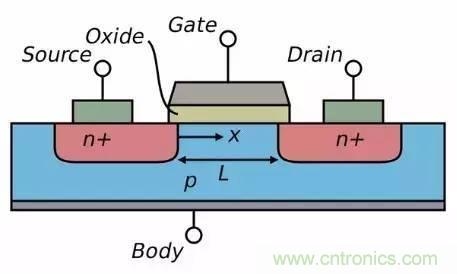

這個(gè)尺寸很重要,因?yàn)榫w管的作用�,簡(jiǎn)單地說(shuō),就是把電子從一端(S)����,通過(guò)一段溝道,送到另一端(D)�,這個(gè)過(guò)程完成之后,信息的傳遞就完成了。因?yàn)殡娮拥乃俣仁怯邢薜?���,在現(xiàn)代晶體管中,一般都是以飽和速度運(yùn)行的����,所以需要的時(shí)間基本就由這個(gè)溝道的長(zhǎng)度來(lái)決定。越短���,就越快��。

這個(gè)溝道的長(zhǎng)度�����,和前面說(shuō)的晶體管的尺寸����,大體上可以認(rèn)為是一致的����。但是二者有區(qū)別�,溝道長(zhǎng)度是一個(gè)晶體管物理的概念,而用于技術(shù)節(jié)點(diǎn)的那個(gè)尺寸,是制造工藝的概念��,二者相關(guān)�����,但是不能完全劃等號(hào)�。

在微米時(shí)代,這個(gè)技術(shù)節(jié)點(diǎn)的數(shù)字越小��,晶體管的尺寸也越小���,溝道長(zhǎng)度也就越小�����。但是在22nm節(jié)點(diǎn)之后�,晶體管的實(shí)際尺寸�����,或者說(shuō)溝道的實(shí)際長(zhǎng)度���,是長(zhǎng)于這個(gè)數(shù)字的���。比方說(shuō)����,英特爾的14nm的晶體管��,溝道長(zhǎng)度其實(shí)是20nm左右���。

這里就涉及到三個(gè)問(wèn)題:

第一���,為什么要把晶體管的尺寸縮小�?以及是按照怎樣的比例縮小的?這個(gè)問(wèn)題就是在問(wèn)����,縮小有什么好處?

第二��, 為什么技術(shù)節(jié)點(diǎn)的數(shù)字不能等同于晶體管的實(shí)際尺寸����?或者說(shuō),在晶體管的實(shí)際尺寸并沒(méi)有按比例縮小的情況下���,為什么要宣稱是新一代的技術(shù)節(jié)點(diǎn)����?這個(gè)問(wèn)題就是在問(wèn)���,縮小有什么技術(shù)困難�����?

第三����, 具體如何縮?。恳簿褪?,技術(shù)節(jié)點(diǎn)的發(fā)展歷程是怎樣的?在每一代都有怎樣的技術(shù)進(jìn)步���?在這里我特指晶體管的設(shè)計(jì)和材料���。

下面盡我所能來(lái)回答,歡迎指正�����。

第一個(gè)問(wèn)題,一部分的答案已經(jīng)說(shuō)了�����,因?yàn)樵叫【驮娇?��。這個(gè)快是可以直接翻譯為基于晶體管的集成電路芯片的性能上去的���。下面以微處理器CPU為例,如下圖所示�����。

上邊這張圖的信息量很大�����,綠色的點(diǎn)�����,代表CPU的時(shí)鐘頻率,越高當(dāng)然越快��?�?梢钥闯鲋钡?004年����,CPU的時(shí)鐘頻率基本是指數(shù)上升的����,背后的主要原因就是晶體管的尺寸縮小。

另外一個(gè)重要的原因是�����,尺寸縮小之后����,集成度(單位面積的晶體管數(shù)量)提升,這有多個(gè)好處�,一來(lái)可以增加芯片的功能,二來(lái)�,根據(jù)摩爾定律,集成度提升的直接結(jié)果是成本的下降���。

這也是為什么半導(dǎo)體行業(yè)50年來(lái)如一日地追求摩爾定律的原因�����,因?yàn)槿绻_(dá)不到這個(gè)標(biāo)準(zhǔn)��,你家的產(chǎn)品成本就會(huì)高于能達(dá)到這個(gè)標(biāo)準(zhǔn)的對(duì)手�����,你家就倒閉了����。

還有一個(gè)原因是晶體管縮小可以降低單個(gè)晶體管的功耗,因?yàn)榭s小的規(guī)則要求�����,同時(shí)會(huì)降低整體芯片的供電電壓���,進(jìn)而降低功耗���。

但也有例外,從物理原理上說(shuō)��,單位面積的功耗并不降低。因此這成為了晶體管縮小的一個(gè)很嚴(yán)重的問(wèn)題����,因?yàn)槔碚撋系挠?jì)算是理想情況,實(shí)際上���,不僅不降低�,反而是隨著集成度的提高而提高的�����。

2000年前后�����,人們已經(jīng)預(yù)測(cè)到�,根據(jù)摩爾定律的發(fā)展�����,如果沒(méi)有什么技術(shù)進(jìn)步的話�,晶體管縮小到2010年前后時(shí),其功耗密度可以達(dá)到火箭發(fā)動(dòng)機(jī)的水平�,這樣的芯片當(dāng)然是不可能正常工作的。即使達(dá)不到這個(gè)水平,溫度太高也會(huì)影響晶體管的性能��。

事實(shí)上�,業(yè)界現(xiàn)在也沒(méi)有找到真正徹底解決晶體管功耗問(wèn)題的方案,實(shí)際的做法是:一方面降低電壓(功耗與電壓的平方成正比)��,一方面不再追求時(shí)鐘頻率�����。因此在上圖中����,2005年以后,CPU頻率不再增長(zhǎng)���,性能的提升主要依靠多核架構(gòu)���。這個(gè)被稱作“功耗墻”,至今仍然存在��,所以你買(mǎi)不到5GHz的處理器���,4G的都幾乎沒(méi)有���。

以上是三個(gè)縮小晶體管的主要誘因���。可以看出���,都是重量級(jí)的提升性能��、功能���、降低成本的方法,所以業(yè)界才會(huì)一直堅(jiān)持到現(xiàn)在�����。

那么是怎樣縮小的呢����?物理原理是恒定電場(chǎng)�,因?yàn)榫w管的物理學(xué)通俗的說(shuō),是電場(chǎng)決定的�,所以只要電場(chǎng)不變,晶體管的模型就不需要改變��,這種方式被證明效果最佳,被稱為Dennard Scaling��,提出者是IBM�����。

電場(chǎng)等于電壓除以尺寸����。既然要縮小尺寸,就要等比降低電壓����。

如何縮小尺寸?簡(jiǎn)單粗暴:將面積縮小到原來(lái)的一半就好了����。面積等于尺寸的平方,因此尺寸就縮小大約0.7���。如果看一下晶體管技術(shù)節(jié)點(diǎn)的數(shù)字:

130nm 90nm 65nm 45nm 32nm 22nm 14nm 10nm 7nm (5nm)

會(huì)發(fā)現(xiàn)是一個(gè)大約以0.7為比的等比數(shù)列?�,F(xiàn)在�����,這只是一個(gè)命名的習(xí)慣���,跟實(shí)際尺寸已經(jīng)有差距了���。

第二個(gè)問(wèn)題,為什么現(xiàn)在的技術(shù)節(jié)點(diǎn)不再直接反應(yīng)晶體管的尺寸呢�����?

原因也很簡(jiǎn)單�,因?yàn)闊o(wú)法做到這個(gè)程度的縮小了。有三個(gè)主要原因:

首先��,原子尺度的計(jì)量單位是埃���,為0.1nm����。

10nm的溝道長(zhǎng)度����,也就只有不到100個(gè)硅原子而已���。未來(lái)晶體管物理模型是這樣的:用量子力學(xué)的能帶論計(jì)算電子的分布���,但是用經(jīng)典的電流理論計(jì)算電子的輸運(yùn)�����。

電子在分布確定之后��,仍然被當(dāng)作一個(gè)粒子來(lái)對(duì)待���,而不是考慮它的量子效應(yīng)。因?yàn)槌叽绱?����,所以不需要�����。但是越小�,就越不行,就需要考慮各種復(fù)雜的物理效應(yīng)�。

其次,即使用經(jīng)典的模型����,性能上也出了問(wèn)題�,這個(gè)叫做短溝道效應(yīng)�,其效果是損害晶體管的性能。

短溝道效應(yīng)其實(shí)很好理解�,通俗地講,晶體管是一個(gè)三個(gè)端口的開(kāi)關(guān)�����,其工作原理是把電子從一端(源端)送到另一端(漏端)���,這是通過(guò)溝道進(jìn)行的�����,另外還有一個(gè)端口(柵端)的作用是�����,決定這條溝道是打開(kāi)的�����,還是關(guān)閉的�。這些操作都是通過(guò)在端口上加上特定的電壓來(lái)完成的�。

晶體管性能依賴的一點(diǎn)是,必須要打得開(kāi)����,也要關(guān)得緊。短溝道器件����,打得開(kāi)沒(méi)問(wèn)題,但是關(guān)不緊�����,原因就是尺寸太小���,內(nèi)部有很多電場(chǎng)上的互相干擾�����,以前都是可以忽略不計(jì)的���,現(xiàn)在則會(huì)導(dǎo)致柵端的電場(chǎng)不能夠發(fā)揮全部的作用,因此關(guān)不緊。關(guān)不緊的后果就是有漏電流����,簡(jiǎn)單地說(shuō)就是不需要、浪費(fèi)的電流�����。

可不能小看這部分電流�,因?yàn)榇藭r(shí)晶體管是在休息,沒(méi)有做任何事情�,卻在白白地耗電。目前�,集成電路中的這部分漏電流導(dǎo)致的能耗,已經(jīng)占到了總能耗的近50%�,所以也是目前晶體管設(shè)計(jì)和電路設(shè)計(jì)的一個(gè)最主要的難題。

第三�����,制造工藝也越來(lái)越難做到那么小的尺寸了�����。

決定制造工藝的最小尺寸的����,叫做光刻機(jī)�。它的功能是���,把預(yù)先印制好的電路設(shè)計(jì),像洗照片一樣洗到晶片表面上去���,在我看來(lái)就是一種bug級(jí)的存在�,因?yàn)橥掏侣史浅5馗?���。否則那么復(fù)雜的集成電路,如何才能制造出來(lái)呢���?比如英特爾的奔騰4處理器�,據(jù)說(shuō)需要30~40多張不同的設(shè)計(jì)模板���,先后不斷地曝光�,才能完成整個(gè)處理器的設(shè)計(jì)印制����。

但是光刻機(jī),顧名思義,是用光的��,當(dāng)然不是可見(jiàn)光���,但總之是光���。

而稍有常識(shí)就會(huì)知道,所有用光的東西�����,都有一個(gè)問(wèn)題�,就是衍射。光刻機(jī)也不例外�。

因?yàn)檫@個(gè)問(wèn)題的制約,任何一臺(tái)光刻機(jī)所能刻制的最小尺寸���,基本上與它所用的光源的波長(zhǎng)成正比����。波長(zhǎng)越小�����,尺寸也就越小,這個(gè)道理是很簡(jiǎn)單的���。

目前的主流生產(chǎn)工藝采用荷蘭艾斯摩爾生產(chǎn)的步進(jìn)式光刻機(jī)�,所使用的光源是193nm的氟化氬(ArF)分子振蕩器產(chǎn)生的���,被用于最精細(xì)尺寸的光刻。

相比之下����,目前的最小量產(chǎn)的晶體管尺寸是20nm (14nm node),已經(jīng)有了10倍以上的差距���。

有人會(huì)問(wèn)����,為何沒(méi)有衍射效應(yīng)呢�����?

答案是業(yè)界10多年來(lái)在光刻技術(shù)上投入了巨資���,先后開(kāi)發(fā)了各種魔改級(jí)別的暴力技術(shù)��,諸如浸入式光刻(把光程放在某種液體里�����,因?yàn)楣獾恼凵渎矢?�,而最小尺寸反比于折射率)����、相位掩模(通過(guò)180度反向的方式來(lái)讓產(chǎn)生的衍射互相抵消,提高精確度)��,等等�����,就這樣一直撐到了現(xiàn)在�,支持了60nm以來(lái)的所有技術(shù)節(jié)點(diǎn)的進(jìn)步。

又有人會(huì)問(wèn)���,為何不用更小波長(zhǎng)的光源呢�����?

答案是���,工藝上暫時(shí)做不到�。

是的���,高端光刻機(jī)的光源��,是世界級(jí)的工業(yè)難題���。

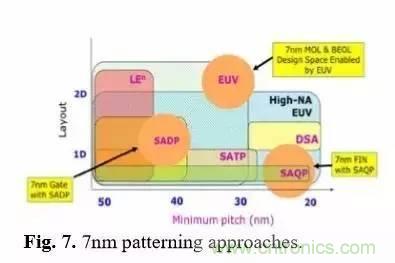

以上就是目前主流的深紫外曝光技術(shù)(DUV)。業(yè)界普遍認(rèn)為��,7nm技術(shù)節(jié)點(diǎn)是它的極限了�����,甚至7nm都不一定能夠做到量產(chǎn)���。下一代技術(shù)仍然在開(kāi)發(fā)之中,被稱為極紫外(EUV)����,其光源降到了13nm。但是別高興地太早�,因?yàn)樵谶@個(gè)波長(zhǎng)����,已經(jīng)沒(méi)有合適的介質(zhì)可以用來(lái)折射光���,構(gòu)成必須的光路了�,因此這個(gè)技術(shù)里面的光學(xué)設(shè)計(jì)���,全部是反射�,而在如此高的精度下���,設(shè)計(jì)如此復(fù)雜的反射光路�����,本身就是難以想象的技術(shù)難題�����。

這還不算(已經(jīng)能克服了)��,最難的還是光源���,雖然可以產(chǎn)生所需的光線��,但是強(qiáng)度遠(yuǎn)低于工業(yè)生產(chǎn)的需求���,造成EUV光刻機(jī)的晶圓產(chǎn)量達(dá)不到要求,換言之���,拿來(lái)用就會(huì)賠本����。一臺(tái)這種機(jī)器就上億美元����。所以EUV還屬于未來(lái)�����。

基于以上三個(gè)原因�,其實(shí)很早開(kāi)始就導(dǎo)致晶體管的尺寸縮小進(jìn)入了深水區(qū)��,越來(lái)越難�,到了22nm之后�,已經(jīng)無(wú)法做大按比例縮小了�,因此就沒(méi)有再追求一定要縮小���,反而是采用了更加優(yōu)化的晶體管設(shè)計(jì),配合CPU架構(gòu)上的多核多線程等一系列技術(shù)�����,繼續(xù)為消費(fèi)者提供相當(dāng)于更新?lián)Q代了的產(chǎn)品性能��。

目前�����,技術(shù)節(jié)點(diǎn)的數(shù)字仍然在縮小�����,但是已然不再等同于晶體管的尺寸,而是代表一系列構(gòu)成這個(gè)技術(shù)節(jié)點(diǎn)的指標(biāo)的技術(shù)和工藝的總和�����。

第三個(gè)問(wèn)題,技術(shù)節(jié)點(diǎn)的縮小過(guò)程中���,晶體管的設(shè)計(jì)是怎樣發(fā)展的。

首先要搞清楚���,晶體管設(shè)計(jì)的思路是什么�。主要的無(wú)非兩點(diǎn):第一提升開(kāi)關(guān)響應(yīng)度�,第二降低漏電流��。

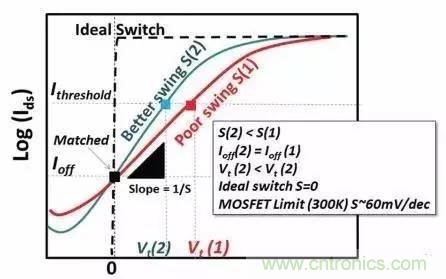

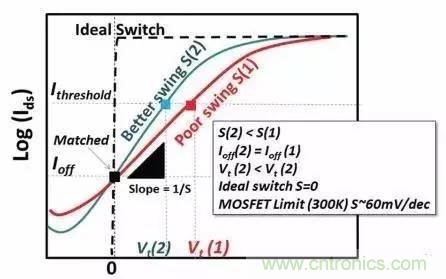

為了講清楚這個(gè)問(wèn)題����,最好的方法是看圖�。晶體管物理的圖,基本上搞清楚一張就足夠了�,就是漏電流-柵電壓的關(guān)系圖,比如下面這種:

橫軸代表柵電壓,縱軸代表漏電流���,并且縱軸一般是對(duì)數(shù)坐標(biāo)�����。

前面說(shuō)過(guò)����,柵電壓控制晶體管的開(kāi)關(guān)����。可以看出���,最好的晶體管,是那種能夠在很小的柵電壓變化內(nèi)�,一下子就從完全關(guān)閉(漏電流為0),變成完全打開(kāi)(漏電流達(dá)到飽和值)���,也就是虛線���。這個(gè)性質(zhì)有多方面的好處,下面會(huì)說(shuō)明��。

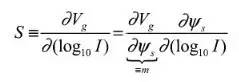

顯然這種晶體管不存在于這個(gè)星球上����。原因是���,在經(jīng)典的晶體管物理理論下,衡量這個(gè)開(kāi)關(guān)響應(yīng)能力的標(biāo)準(zhǔn)����,叫做Subthreshold Swing(SS���,不是黨衛(wèi)軍...)���,有一個(gè)極限值,約為60�,背后的原因就不細(xì)說(shuō)了�。

根據(jù)英特爾的數(shù)據(jù),最新的14nm晶體管�,這個(gè)數(shù)值大概是70左右(越低越好)���。

并且��,降低這個(gè)值,和降低漏電流、提升工作電流(提高速度)���、降低功耗等要求,是等同的���,因?yàn)檫@個(gè)值越低�����,在同樣的電壓下���,漏電流就越低。而為了達(dá)到同樣的工作電流���,需要的電壓就越低,這樣等同于降低了功耗��。所以說(shuō)這個(gè)值是晶體管設(shè)計(jì)里面最重要的指標(biāo)��,不過(guò)分���。

圍繞這個(gè)指標(biāo)����,以及背后的晶體管性能設(shè)計(jì)的幾個(gè)目標(biāo)���,大家都做了哪些事情呢�����?

先看工業(yè)界���,畢竟實(shí)踐是檢驗(yàn)真理的唯一標(biāo)準(zhǔn)。下面是我的記憶���,和節(jié)點(diǎn)的對(duì)應(yīng)不一定完全準(zhǔn)確,但具體的描述應(yīng)該沒(méi)錯(cuò):

65nm引入Ge strained溝道��。

strain我不知道如何翻譯成中文詞匯�����,但是其原理是通過(guò)在適當(dāng)?shù)牡胤綋诫s一點(diǎn)點(diǎn)的鍺到硅里面去��,鍺和硅的晶格常數(shù)不同��,因此會(huì)導(dǎo)致硅的晶格形狀改變�����,而根據(jù)能帶論���,這個(gè)改變可以在溝道的方向上提高電子的遷移率��,而遷移率高�����,就會(huì)提高晶體管的工作電流�。而在實(shí)際中���,人們發(fā)現(xiàn)��,這種方法對(duì)于空穴型溝道的晶體管(pmos)��,比對(duì)電子型溝道的晶體管(nmos),更加有效��。

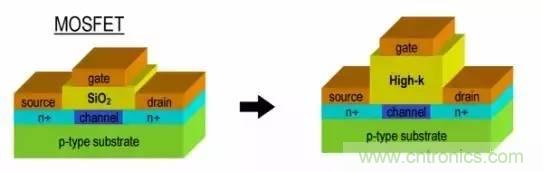

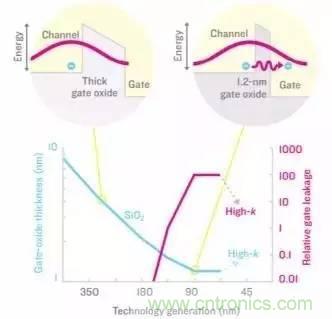

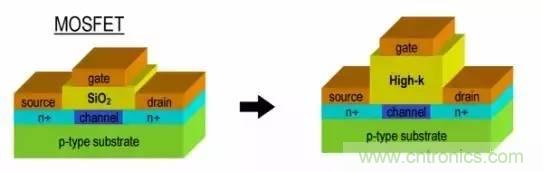

45nm引入了高k值絕緣層/金屬柵極配置。

這個(gè)也是一個(gè)里程碑的成果��,我在念書(shū)的時(shí)候曾經(jīng)有一位幫他搬過(guò)磚的教授����,當(dāng)年是在英特爾開(kāi)發(fā)了這項(xiàng)技術(shù)的團(tuán)隊(duì)的主要成員之一���,因此對(duì)這一點(diǎn)提的特別多,耳濡目染就記住了�����。

這是兩項(xiàng)技術(shù)����,但其實(shí)都是為了解決同一個(gè)問(wèn)題:即在很小的尺寸下,如何保證柵極有效的工作�����。

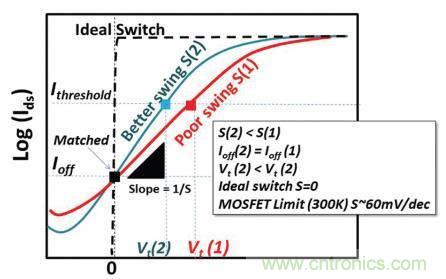

前面沒(méi)有細(xì)說(shuō)晶體管的結(jié)構(gòu)���,下面補(bǔ)一張圖:

這是一個(gè)最基本的晶體管的結(jié)構(gòu)示意圖�,現(xiàn)在的晶體管早就不長(zhǎng)這樣了�����,但是任何半導(dǎo)體物理都是從這兒開(kāi)始講起的���,所以這是“標(biāo)配版”的晶體管�����,又被稱為體硅(bulk)晶體管����。

gate就是柵�����。

其中有一個(gè)oxide��,絕緣層����,前面沒(méi)有提到,但是卻是晶體管所有的構(gòu)件中�����,最關(guān)鍵的一個(gè)��。它的作用是隔絕柵極和溝道��。因?yàn)闁艠O開(kāi)關(guān)溝道,是通過(guò)電場(chǎng)進(jìn)行的����,電場(chǎng)的產(chǎn)生又是通過(guò)在柵極上加一定的電壓來(lái)實(shí)現(xiàn)的,但是歐姆定律告訴我們�����,有電壓就有電流��。如果有電流從柵極流進(jìn)了溝道����,那么還談什么開(kāi)關(guān)?早就漏了�。

所以需要絕緣層����。為什么叫oxide(or "dielectric")而不叫insulator呢?因?yàn)樽钤绲慕^緣層就是和硅非常自然地共處的二氧化硅����,其相對(duì)介電常數(shù)(衡量絕緣性的�����,越高�����,對(duì)晶體管性能來(lái)說(shuō),越好)約是3.9���。一個(gè)好的絕緣層是晶體管的生命線�����,這個(gè)“好”的定義在這里不多說(shuō)了����,但是要說(shuō)明�,硅天然就具有這么一個(gè)性能:超級(jí)好的絕緣層,對(duì)于半導(dǎo)體工業(yè)來(lái)說(shuō)�����,是一件有歷史意義的事情�。

有人曾經(jīng)感慨�����,說(shuō)上帝都在幫助人類發(fā)明集成電路���,首先給了那么多的沙子(硅晶圓的原料),又給了一個(gè)完美的自然絕緣層��。所以至今����,硅極其難被取代,一個(gè)重要原因就是����,作為制造晶體管的材料,其綜合性能太完美了�����。

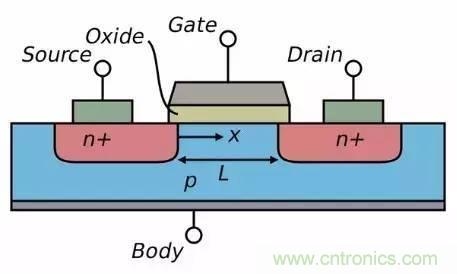

二氧化硅雖好��,在尺寸縮小到一定限度時(shí)��,也出現(xiàn)了問(wèn)題��。別忘了縮小的過(guò)程中,電場(chǎng)強(qiáng)度是保持不變的����,在這樣的情況下�����,從能帶的角度看�,因?yàn)殡娮拥牟▌?dòng)性,如果絕緣層很窄很窄的話���,那么有一定的幾率電子會(huì)發(fā)生隧穿效應(yīng)而越過(guò)絕緣層的能帶勢(shì)壘����,產(chǎn)生漏電流�。

可以想象為穿過(guò)一堵比自己高的墻����。這個(gè)電流的大小和絕緣層的厚度,以及絕緣層的“勢(shì)壘高度”���,成負(fù)相關(guān)。因此厚度越小�,勢(shì)壘越低,這個(gè)漏電流越大�,對(duì)晶體管越不利����。

另一方面,晶體管的開(kāi)關(guān)性能����、工作電流等,都需要擁有一個(gè)很大的絕緣層電容��。實(shí)際上����,如果這個(gè)電容無(wú)限大的話�,那么就會(huì)達(dá)到理想化的60的那個(gè)SS指標(biāo)。

這里說(shuō)的電容都是指單位面積的電容����。這個(gè)電容等于介電常數(shù)除以絕緣層的厚度����。顯然,厚度越小����,介電常數(shù)越大�����,對(duì)晶體管越有利�。

可以看出,這里已經(jīng)出現(xiàn)了一對(duì)設(shè)計(jì)目標(biāo)上的矛盾����,那就是絕緣層的厚度要不要繼續(xù)縮小��。實(shí)際上在這個(gè)節(jié)點(diǎn)之前��,二氧化硅已經(jīng)縮小到了不到兩個(gè)納米的厚度��,也就是十幾個(gè)原子層的厚度���,漏電流的問(wèn)題已經(jīng)取代了性能的問(wèn)題,成為頭號(hào)大敵�����。

于是聰明絕頂?shù)娜祟愰_(kāi)始想辦法�����。人類很貪心的���,既不愿意放棄大電容的性能增強(qiáng)�����,又不愿意冒漏電的風(fēng)險(xiǎn)�����。于是人類說(shuō)�����,如果有一種材料���,介電常數(shù)很高,同時(shí)能帶勢(shì)壘也很高���,那么是不是就可以在厚度不縮小的情況下(保護(hù)漏電流)�����,繼續(xù)提升電容(提高開(kāi)關(guān)性能)呢�����?

于是大家就開(kāi)始找����,用幾乎暴力的方法���,找了許多種奇奇怪怪的材料��,終于最后經(jīng)過(guò)驗(yàn)證�����,確定使用一種名為HfO2的材料����。這個(gè)元素我以前聽(tīng)都沒(méi)有聽(tīng)過(guò)���,中文念什么我都說(shuō)不上來(lái)����。就是這么牛���。這個(gè)就叫做high-k�,這里的k是相對(duì)介電常數(shù)(相對(duì)于二氧化硅的而言)。

當(dāng)然��,這個(gè)工藝的復(fù)雜程度����,遠(yuǎn)遠(yuǎn)超過(guò)這里描述的這么簡(jiǎn)單�。具備high-k性質(zhì)的材料很多,但是最終被采用的材料���,一定要具備許多優(yōu)秀的電學(xué)性質(zhì)�����,因?yàn)槎趸枵娴氖且豁?xiàng)非常完美的晶體管絕緣層材料��,而且制造工藝流程和集成電路的其它制造步驟可以方便地整合�,所以找到這樣一項(xiàng)各方面都符合半導(dǎo)體工藝制造的要求的高性能絕緣層材料�,是一件了不起的工程成就。

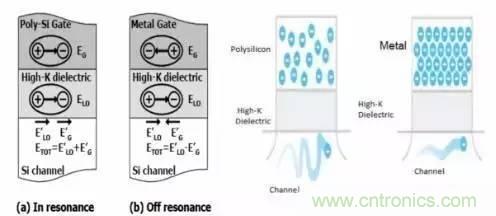

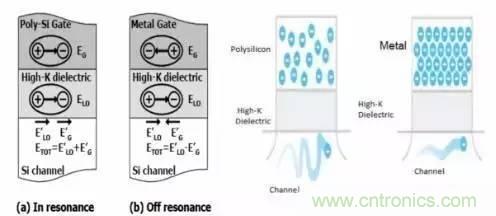

至于金屬柵�����,是與high-k配套的一項(xiàng)技術(shù)。在晶體管的最早期�����,柵極是用鋁制作���,后來(lái)經(jīng)過(guò)發(fā)展,改用重?fù)诫s多晶硅制作����,因?yàn)楣に嚭?jiǎn)單,性能好���。到了high-k這里�,大家發(fā)現(xiàn)���,high-k材料有兩個(gè)副作用�����,一是會(huì)莫名其妙地降低工作電流�����,二是會(huì)改變晶體管的閾值電壓�。閾值電壓就是把晶體管的溝道打開(kāi)所需要的最小電壓值,這個(gè)值是非常重要的晶體管參數(shù)���。

這個(gè)原理不細(xì)說(shuō)了(其實(shí)是說(shuō)不清楚才對(duì)吧哈哈...?)�,主要原因是�����,high-k材料會(huì)降低溝內(nèi)的道載流子遷移率��,并且影響在界面上的費(fèi)米能級(jí)的位置��。載流子遷移率越低��,工作電流就越低�����,而所謂的費(fèi)米能級(jí)���,是從能帶論的圖像上來(lái)解釋半導(dǎo)體電子分布的一種分析方法,簡(jiǎn)單地說(shuō)�,它的位置會(huì)影響晶體管的閾值電壓����。

這兩個(gè)問(wèn)題的產(chǎn)生�����,都和high-k材料內(nèi)部的偶極子分布有關(guān)�����。偶極子是一端正電荷一端負(fù)電荷的一對(duì)電荷系統(tǒng)�����,可以隨著外加電場(chǎng)的方向而改變自己的分布�,high-k材料的介電常數(shù)之所以高的原因��,就跟內(nèi)部的偶極子有很大關(guān)系�����。所以這是一把雙刃劍��。

于是人類又想����,就想到了用金屬做柵極��,因?yàn)榻饘俚淖杂呻姾蓾舛葮O高(超過(guò)10^20)�����,而且有鏡像電荷效應(yīng)�����,可以中和掉high-k材料的絕緣層里的偶極子對(duì)溝道和費(fèi)米能級(jí)的影響��。這樣一來(lái)就兩全其美啦�。

至于這種或這幾種金屬究竟是什么����,很抱歉�,除了掌握技術(shù)的那幾家企業(yè)之外,外界沒(méi)有人知道�,是商業(yè)機(jī)密��。

有朋友補(bǔ)充說(shuō)����,這種金屬是鎢���,我查閱到資料也提到是鎢�;鎢本身也用在后端的via中���; 但是在這個(gè)問(wèn)題上我有些保留,主要原因是4點(diǎn):

第一����, 我自己上課的時(shí)候��,有多位教授都明確提到過(guò)���,關(guān)于這個(gè)metal gate的資料外界知之甚少����,至少他們自己不知道,或因?yàn)槟撤N原因而不愿意說(shuō)���;

第二��,從原理上說(shuō),對(duì)于NMOS和PMOS���,因?yàn)樗璧墓瘮?shù)是不一樣的,所以單一的一種金屬無(wú)論如何是不可能滿足整個(gè)high-k工藝的需求�����,即使確實(shí)是鎢�,也需要進(jìn)行work function engineering�;

第三���, 也有很多資料提到了別的材料�,譬如說(shuō)TiN 系列作為metal gate�;

第四�, 或許也是最令人疑惑的,就是在我查閱過(guò)的資料中�,雖然Intel很早就說(shuō)使用了HfO2作為high-k材料,但是Intel自己卻沒(méi)有透露這種或這幾種金屬是什么�����,譬如它在2008年發(fā)表的iedm的文章:

http://download.intel.com/pressroom/kits/advancedtech/pdfs/Natarajan_iedm_2008_text.pdf��,沒(méi)有提及具體的材料,而是以"metal gate"作為代稱���。Mark Bohl在2007年發(fā)表的文章中,也明確說(shuō)到如下的信息:

“Because the electrical characteristics of the gates of NMOS and PMOS transistors are different, they actually needed not one metal but two—one for NMOS and one for PMOS.”

“But by themselves, none had exactly the work function of the doped silicon, so we had to learn to change the work function of metals to suit our needs.”

“We cannot disclose the exact makeup of our metal layers, because after all, the IC industry is very competitive!”

更新的資料中��,似乎也沒(méi)有找到相關(guān)的信息����,而是多以WFM (work function metal)作為指代�。雖然在研究界有過(guò)關(guān)于W��、TiN等多種材料的不少研究論文發(fā)表����,但是我自己是無(wú)力確認(rèn)關(guān)于這個(gè)metal gate材料的信息來(lái)源是什么����。因?yàn)楸救瞬⒉粡氖戮w管制造或設(shè)計(jì)的研究工作,無(wú)力回答這個(gè)問(wèn)題�。因此希望能有知情的朋友進(jìn)行補(bǔ)充,并且提供來(lái)源���。

于是摩爾定律再次勝利。

32nm第二代high-k絕緣層/金屬柵工藝����。

在45nm時(shí)代�����,英特爾取得了巨大的成功(在很多晶體管�、微處理器的發(fā)展圖上�,45nm這一代的晶體管,會(huì)在功耗�、性能等方面突然出現(xiàn)一個(gè)較大的進(jìn)步折線),32nm時(shí)候繼續(xù)在基礎(chǔ)上改換更好的材料�����,繼續(xù)了縮小尺寸的老路�。當(dāng)然���,前代的Ge strain工藝也是繼續(xù)使用的。

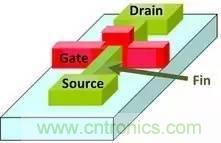

22nm FinFET(英特爾稱為T(mén)ri-gate)���,三柵極晶體管。

這一代的晶體管�����,在架構(gòu)上進(jìn)行了一次變革�。變革的最早設(shè)計(jì)可以追溯到伯克利的胡正明教授2000左右提出的三柵極和環(huán)柵晶體管物理模型���,后來(lái)被英特爾變?yōu)榱爽F(xiàn)實(shí)����。

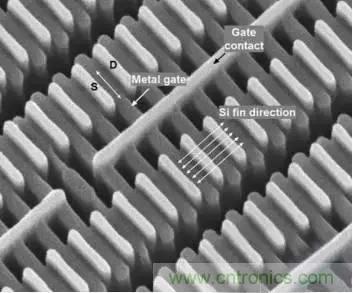

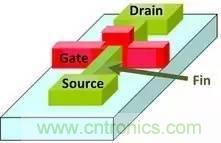

FinFET 一般模型長(zhǎng)這樣�。它的實(shí)質(zhì)上是增加了一個(gè)柵極����。

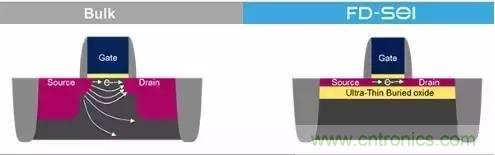

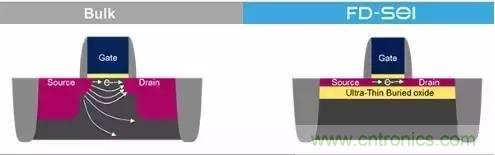

為什么要這么做呢�?直觀地說(shuō)��,如果看前面的那張“標(biāo)配版”的晶體管結(jié)構(gòu)圖����,在尺寸很短的晶體管里面��,因?yàn)槎虦系佬?yīng)��,漏電流是比較嚴(yán)重的��。而大部分的漏電流��,是通過(guò)溝道下方的那片區(qū)域流通的。

溝道在圖上并沒(méi)有標(biāo)出來(lái),是位于氧化絕緣層以下���、硅晶圓表面的非常非常薄(一兩個(gè)納米)的一個(gè)窄窄的薄層�����。溝道下方的區(qū)域被稱為耗盡層����,就是大部分的藍(lán)色區(qū)域�。

于是有人就開(kāi)始想啊,既然電子是在溝道中運(yùn)動(dòng)��,那么我為何非要在溝道下面留有這么一大片耗盡層呢�����?當(dāng)然這是有原因的,因?yàn)槲锢砟P托枰@片區(qū)域來(lái)平衡電荷�。但是在短溝道器件里面,沒(méi)有必要把耗盡層和溝道放在一起��,等著漏電流白白地流過(guò)去����。

于是有人(IBM)開(kāi)了一個(gè)腦洞:把這部分硅直接拿掉�����,換成絕緣層��,絕緣層下面才是剩下的硅,這樣溝道就和耗盡層分開(kāi)了�,因?yàn)殡娮觼?lái)源于兩極��,但是兩極和耗盡層之間�,被絕緣層隔開(kāi)了,這樣除了溝道之外�,就不會(huì)漏電啦��。比如這樣:

這個(gè)叫做SOI(絕緣層上硅)��,雖然沒(méi)有成為主流�����,但是因?yàn)橛衅鋬?yōu)勢(shì)����,所以現(xiàn)在還有制造廠在搞����。

于是有人(英特爾)又想了��,既然都是拿掉耗盡層的硅�����,插入一層氧化層����,那么為什么非要放上一堆沒(méi)用的硅在下面��,直接在氧化層底下���,再弄一個(gè)柵極�����,兩邊夾著溝道,豈不是更爽����?你看你IBM���,就是沒(méi)雄心。

但是英特爾還覺(jué)得不夠�,又想�,既然如此,有什么必要非得把氧化層埋在硅里面�����?我把硅弄出來(lái)�����,周圍三明治一樣地包裹上絕緣層����,外面再放上柵極��,豈不是爽爆��?

于是就有了FinFET���,上面這種。FinFET牛逼的地方在于�,不僅大大降低了漏電流,而且因?yàn)槎嘁粋€(gè)柵極�,這兩個(gè)柵極一般都是連在一起的�,大大增加了前面說(shuō)過(guò)的那個(gè)絕緣層電容,也就大大提升了晶體管的開(kāi)關(guān)性能�。所以又是一次革命式的進(jìn)步����。

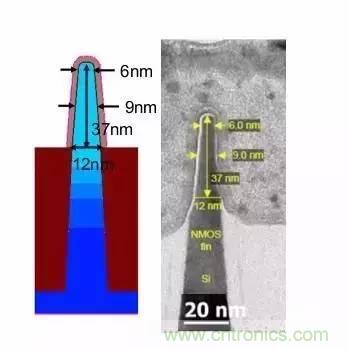

這個(gè)設(shè)計(jì)其實(shí)不難想到��,難的是��,能夠做到�。為什么呢?因?yàn)樨Q起來(lái)的那一部分硅��,也就是用作溝道的硅����,太薄了��,只有不到10個(gè)納米,不僅遠(yuǎn)小于晶體管的最小尺寸��,也遠(yuǎn)小于最精密的光刻機(jī)所能刻制的最小尺寸�。于是如何把這個(gè)Fin給弄出來(lái)��,還得弄好�,成了真正的難題�。

英特爾的做法是很聰明的,解釋起來(lái)需要很多張工藝流程圖�,不多說(shuō)���,但是基本原理是��,這部分硅不是光刻出來(lái)的�,而是長(zhǎng)出來(lái)的���。它先用普通精度的光刻刻出一堆“架子,然后在沉淀一層硅�,在架子的邊緣就會(huì)長(zhǎng)出一層很薄的硅���,然后再用選擇性的刻蝕把多余的材料弄走��,剩下的就是這些立著的、超薄的硅Fin了���。當(dāng)時(shí)我聽(tīng)說(shuō)這套方法的時(shí)候�,徹底跪了����,這智商太碾壓人了。

FinFET的工藝流程

制作FinFET的工藝流程具體是怎樣的呢�����?筆者并非這方面的專家���,所知有限����。盡所能查閱了一些資料之后,把相關(guān)的一些信息整理在下面�����,供大家參考。

在2016年8月的這篇訪談中����,Intel的Mark Bohl (Senior fellow and director of process architecture and integration)談到了Intel的FinFET技術(shù)����,以及對(duì)于10nm制程的技術(shù)展望。在其中,他提到Intel將會(huì)繼續(xù)使用SADP (Self-Aligned Double Patterning)工藝���。

Double Patterning是可以提高光刻最小精度的,是目前主流采用的一種技術(shù)��,有很多個(gè)版本��。它的原理是這樣的���,譬如說(shuō)��,Intel是采用193nm的浸入式光刻來(lái)處理最高精度需求的步驟���,這個(gè)技術(shù)的最小尺寸大約是80~90nm之間。如果使用Double Patterning的話呢��,則可以將這個(gè)精度提高到約40nm左右�����。

這個(gè)在原理上是很容易理解�,如果先pattern一批80nm精度的圖樣,然后再交錯(cuò)著pattern一批80nm精度的圖樣�,在兩次光刻之后����,圖樣的精度�����,以pitch來(lái)衡量的話�,就會(huì)是原來(lái)的精度的一半。這個(gè)過(guò)程在維基百科中就有說(shuō)明�,大家可以直接查閱

Multiple patterning��。

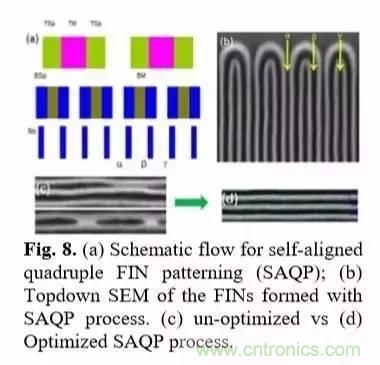

Self-Aligned Double Patterning是其中的一種技術(shù)�,它只需要一次光刻步驟就能完成��,而且從原理上說(shuō)����,是可以用來(lái)制作fin的(制作fin的這個(gè)步驟叫做active fin formation)����。我在上一些相關(guān)的器件和工藝課程的時(shí)候,自己的教授也有提到這個(gè)工藝是被用來(lái)制作fin的�����。但是在這方面����,我并沒(méi)有找到直接的資料���,來(lái)自Intel 或別的幾個(gè)大廠,來(lái)說(shuō)明自己的active fin formation具體是怎么做的��,因此這只能算是一個(gè)合理的猜測(cè)���。

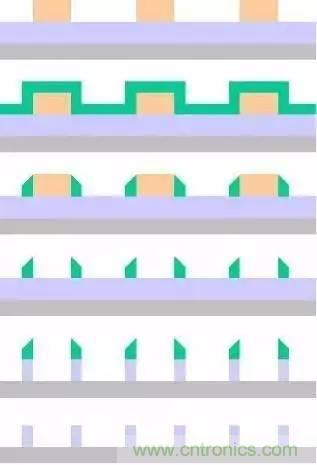

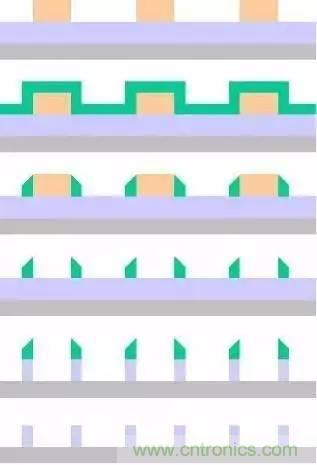

在這個(gè)過(guò)程中,首先會(huì)沉積一層hard mask����,又被稱作mandral的材料����,比如Si3N4之類的。這層材料以普通精度的光刻進(jìn)行pattern�。mandral在被pattern之后,就被稱作spacer�����。然后再生長(zhǎng)一層絕緣層材料�����,譬如二氧化硅��,被稱作film。

可以通過(guò)控制這個(gè)生長(zhǎng)過(guò)程的時(shí)間����,來(lái)控制最終的fin的厚度W�����。然后對(duì)film進(jìn)行刻蝕�,將所有水平方向的材料刻蝕掉���,只剩下沿著spacer的邊緣所生長(zhǎng)出來(lái)的那部分��,之后再以選擇性的刻蝕將spacer材料移除,只剩下這層sidewall film����。最后就是對(duì)底下的硅材料進(jìn)行刻蝕,這樣相當(dāng)于用這層film做了mask�。

接下來(lái)�����,為了保證isolation�����,還需要再生長(zhǎng)一層絕緣材料二氧化硅�,這個(gè)步驟要求很高���,因?yàn)閒in和fin之間的那段空間���,高寬比是很大的,需要讓二氧化硅完全填充這個(gè)空隙����,所以這個(gè)步驟被稱作conformal coating����。

顯然這個(gè)步驟之后,硅片的表面是不平整的�,因此需要進(jìn)行一次CMP (Chemical Mechanical Polishing)����,就是通過(guò)添加一定的研磨劑�,用機(jī)械研磨的方式將整個(gè)晶圓的表面給弄平整。

最后就是再對(duì)二氧化硅材料進(jìn)行一次刻蝕����,通過(guò)控制這次刻蝕的時(shí)間�,可以控制露出來(lái)的fin的高度H。在這個(gè)fin上面,再用ALD (Atomic Layer Deposition)等步驟沉積high-k材料等柵極的stack��,就基本完成了這部分的制作���。

上面這個(gè)工藝確實(shí)是存在的���,也是被采用的,然而關(guān)于它有一個(gè)問(wèn)題����,就是我所能找到的資料���,似乎顯示這個(gè)工藝是被IBM���、三星這系列的廠�����,用在SOI的finfet上面���。

前面提到過(guò)SOI的概念����,這里應(yīng)該補(bǔ)充一下����,其實(shí)SOI和finfet并不是兩種對(duì)立的技術(shù)���,之前的比較���,只是為了方便從晶體管物理的角度解釋兩種技術(shù)的思路是什么。finfet也是可以制作在SOI晶圓上面的��,這是三星它們的做法��。

但是Intel似乎并沒(méi)有采用這種做法,出于成本的考慮(SOI晶圓比較貴)���,Intel使用的是bulk finfet�����,溝道底下是沒(méi)有埋絕緣層的����。那么在這個(gè)制程下面��,active fin formation是否也是用SADP這樣的工藝制備的�?我沒(méi)有找到直接的資料證據(jù)�����。

雖然在一些采訪和報(bào)道中,Intel提到自己是用了SADP工藝���,但是這個(gè)工藝并不限于制作fin���,也可以用在制作柵極的pattern以及后端的via, interconnect上面��,因此我不能確定Intel 是怎么做的����。

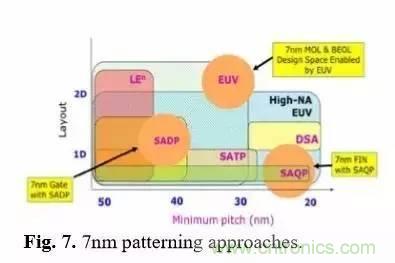

三星在IEDM上發(fā)表過(guò)他們最新的7nm工藝晶體管的報(bào)告中的幾張圖,概述了三星IBM(這倆是一家人...)這個(gè)系列的工藝制程的思路��,它們是這樣考慮的:

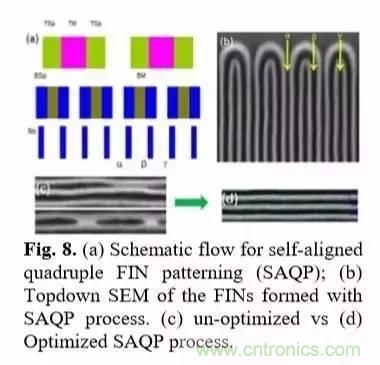

可以看到三星是用SAQP(self-aligned quadruple patterning, 和SADP流程基本一樣����,而又增加了一次光刻�����,因此最小尺寸進(jìn)一步縮小 )來(lái)進(jìn)行7nm fin制備�,如下圖所示:

它也提到了整個(gè)流程���,可是我自己完全看不懂@_@

臺(tái)積電在同一個(gè)會(huì)議中也發(fā)表了7nm,但是語(yǔ)焉不詳�。Intel則沒(méi)有發(fā)表。在Intel發(fā)表的14nm晶體管的文章中�����,同樣只有一句話提到使用了SADP工藝�����,但是并沒(méi)有像三星這樣細(xì)致地說(shuō)明工藝步驟���,而是直接開(kāi)始講晶體管的性能,所以在這方面的信息很少�����。

需要說(shuō)明一下�,無(wú)論是哪個(gè)工藝�����,其實(shí)一開(kāi)始都不是這些公司自己發(fā)明的��,譬如說(shuō),胡正明教授就曾經(jīng)發(fā)表過(guò)SADP相關(guān)的文章�����,那是早在2006年finfet出來(lái)之前多年�����。

這些公司看重了某個(gè)工藝的前景(能不能scale��,成本問(wèn)題���,等等),然后將它整合到自己積累多年的制作流程中去��,推出新一個(gè)節(jié)點(diǎn)的制程��。因?yàn)橥瓿梢粋€(gè)工藝的設(shè)備成本是極其高昂的�,所以往往需要提前多年就做好規(guī)劃���。

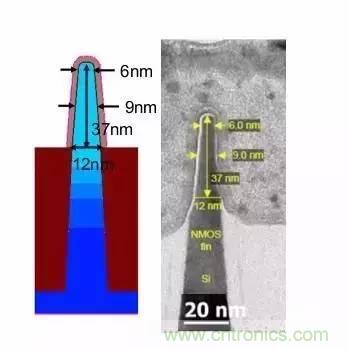

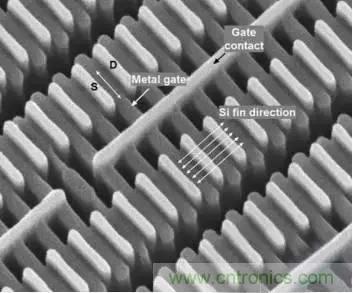

14nm 繼續(xù)FinFET。下面是英特爾的14nm晶體管的SEM橫截面圖����,大家感受一下,fin的寬度平均只有9nm��。

當(dāng)然���,在所有后代的技術(shù)節(jié)點(diǎn)中�,前代的技術(shù)也是繼續(xù)整合采用的��。所以現(xiàn)在����,在業(yè)界和研究界�,一般聽(tīng)到的晶體管�,都被稱作high-k/metal gate Ge-strained 14 nm FinFET,整合了多年的技術(shù)精華��。

而在學(xué)術(shù)界����,近些年陸續(xù)搞出了各種異想天開(kāi)的新設(shè)計(jì),比如隧穿晶體管���,負(fù)電容效應(yīng)晶體管�����,碳納米管��,等等���。

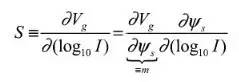

所有這些設(shè)計(jì),基本是4個(gè)方向:材料��、機(jī)理��、工藝�、結(jié)構(gòu)��。而所有的設(shè)計(jì)方案��,其實(shí)可以用一條簡(jiǎn)單的思路概括,就是前面提到的那個(gè)SS值的決定公式��,里面有兩項(xiàng)相乘組成:

因此�,要么改善晶體管的靜電物理(electrostatics),這是其中一項(xiàng)��,要么改善溝道的輸運(yùn)性質(zhì)(transport)���,這是另一項(xiàng)��。

而晶體管設(shè)計(jì)里面�,除了考慮開(kāi)關(guān)性能之外�,還需要考慮另一個(gè)性能,就是飽和電流問(wèn)題�。很多人對(duì)這個(gè)問(wèn)題有誤解���,以為飽不飽和不重要���,其實(shí)電流能飽和才是晶體管能夠有效工作的根本原因,因?yàn)椴伙柡偷脑?�,晶體管就不能保持信號(hào)的傳遞����,因此無(wú)法攜帶負(fù)載�����,換言之只中看,不中用����,放到電路里面去���,根本不能正常工作的����。

舉個(gè)例子,有段時(shí)間石墨烯晶體管很火����,石墨烯作溝道的思路是第二項(xiàng)���,就是輸運(yùn)�,因?yàn)槭┑碾娮舆w移率遠(yuǎn)遠(yuǎn)地完爆硅���。但直到目前,石墨烯晶體管還沒(méi)有太多的進(jìn)展����,因?yàn)槭┯袀€(gè)硬傷,就是不能飽和電流��。但是��,去年貌似聽(tīng)說(shuō)有人能做到調(diào)控石墨烯的能帶間隙打開(kāi)到關(guān)閉�����,石墨烯不再僅僅是零帶隙����,想來(lái)這或許會(huì)在晶體管材料方面產(chǎn)生積極的影響��。

在去年的IEDM會(huì)議上���,臺(tái)積電已經(jīng)領(lǐng)先英特爾,發(fā)布了7nm技術(shù)節(jié)點(diǎn)的晶體管樣品�,而英特爾已經(jīng)推遲了10nm的發(fā)布��。當(dāng)然���,兩者的技術(shù)節(jié)點(diǎn)的標(biāo)準(zhǔn)不一樣,臺(tái)積電的7nm其實(shí)相當(dāng)于英特爾的10nm,但是臺(tái)積電率先拿出了成品��。三星貌似也在會(huì)上發(fā)表了自己的7nm產(chǎn)品。

可以看出�����,摩爾定律確實(shí)放緩了��,22nm是在2010左右出來(lái)的�,到了現(xiàn)在�����,技術(shù)節(jié)點(diǎn)并沒(méi)有進(jìn)步到10nm以下�����。去年����,ITRS已經(jīng)宣布不再制定新的技術(shù)路線圖���,換言之�����,權(quán)威的國(guó)際半導(dǎo)體機(jī)構(gòu)已經(jīng)不認(rèn)為�����,摩爾定律的縮小可以繼續(xù)下去了。

這就是技術(shù)節(jié)點(diǎn)的主要現(xiàn)狀�。

技術(shù)節(jié)點(diǎn)不能進(jìn)步,是不是一定就是壞事���?其實(shí)不一定。28nm這個(gè)節(jié)點(diǎn)���,其實(shí)不屬于前面提到的標(biāo)準(zhǔn)的dennard scaling的一部分,但是這個(gè)技術(shù)節(jié)點(diǎn)�����,直到現(xiàn)在�����,仍然在半導(dǎo)體制造業(yè)界占據(jù)了很大的一塊市場(chǎng)份額�����。

臺(tái)積電����、中芯國(guó)際等這樣的大代工廠��,都是在28nm上玩得很轉(zhuǎn)的�。為何呢�����?因?yàn)檫@個(gè)節(jié)點(diǎn)被證明是一個(gè)在成本���、性能、需求等多方面達(dá)到了比較優(yōu)化的組合的一個(gè)節(jié)點(diǎn)����,很多芯片產(chǎn)品,并不需要使用過(guò)于昂貴的FinFET技術(shù)���,28nm能夠滿足自己的需求����。

但是有一些產(chǎn)品���,比如主流的CPU、GPU����、FPGA��、memory��,其性能的提升有相當(dāng)一部分來(lái)自于工藝的進(jìn)步�����。所以再往后如何繼續(xù)提升這些產(chǎn)品的性能����,是很多人心中的問(wèn)號(hào)��,也是新的機(jī)會(huì)����。

推薦閱讀: